APIX2 High Speed Mezzanine Card

ADK_HSMC

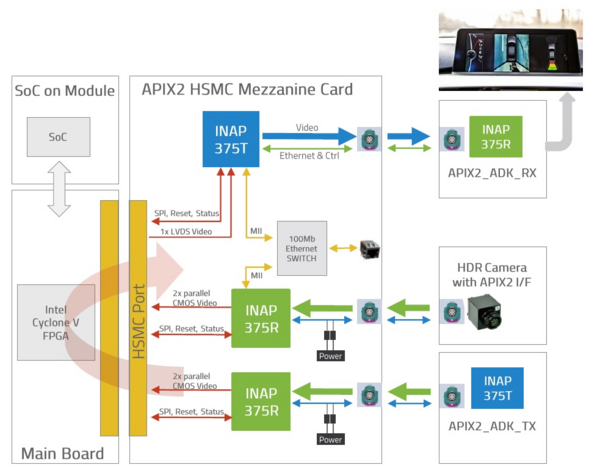

The Inova Semiconductors APIX2 High Speed Mezzanine Card is a transceiver board to simultaneously stream multiple digital video signals as well as 100 Mbps bidirectional Ethernet data traffic and SPI control data over robust 3 Gbps Automotive Pixel Link (APIX) cable connections into and out of a FPGA. It can be connected to any Intel FPGA motherboard with HSMC connector.

The two receiver devices accept video streams with resolutions of up 1600x600 pixels and refresh rates of up to 100Hz. Their flexible video interface is configurable to handle 1 or 2 independent video streams each, which gives a total of up to 4 video input streams.

In camera applications, the cameras can be powered remotely through Power over APIX.

The transmitter can be used to send a 18 or 24bit video with a resolution of up to 1600x600 pixels, 24 Bit color depth and refresh rates of up to 100Hz to a display using the openLDI interface.

The Ethernet port allows to send and receive data traffic over the APIX2 link of the transmitter and receiver #1. It can be used to additionally send IP video traffic over the APIX2 links.

Download APIX2 HSMC Card Flyer

Subscribe to product update notifications: Login or register.

To download the ADK User Manual please login.

APIX2 transmitter

• One INAP375TAQ transmitter with APIX2 serial output

• HSD® (High Speed Data) connector for QSTP cable.

• LVDS interface via the HSMC connector from the FPGA.

• SPI port and STATUS pin connected to the FPGA.

• Media Independent Interface (MII) to the Ethernet Switch

APIX2 receivers

• Two INAP375RAQ receivers with APIX2 serial inputs.

• Two HSD® (High Speed Data) connectors for QSTP cable.

• Parallel video interface of each receiver to the FPGA via the HSMC connector.

• SPI ports and STATUS pins connected to the FPGA.

• Receiver #1 is connected via Media Independent Interface (MII) to the Ethernet Switch

• Power regulator to supply Power over APIX (PoA) towards the cameras

Ethernet Switch

• RJ45 10/100 Mbps Ethernet port

• Onboard Ethernet Switch connected via MII to the APIX2 transmitter and APIX2 receiver #1

TOOL |

DESCRIPTION |

DOWNLOAD |

|---|---|---|

Intel FPGA design store |

Cyclone V SoC Development Kit and SoC Embedded Design Suite |

|

config file |

TOOL |

CONTENT AND DESCRIPTION |

ORDER ID |

|---|---|---|

APIX2 HSMC |

APIX2 High Speed Mezzanine Card for Intel FPGA Development Kit |

ADK_HSMC |